Come afferma IBM Research, siamo solo all’inizio di una rivoluzione dell’intelligenza artificiale che ridefinirà il nostro modo di vivere e lavorare. In particolare, le reti neurali profonde (DNN) hanno rivoluzionato il campo dell’AI e stanno guadagnando sempre più importanza con l’avvento dei modelli foundation e dell’AI generativa. Ma l’esecuzione di questi modelli su architetture informatiche digitali tradizionali ne limita le prestazioni e l’efficienza energetica, secondo IBM.

Ci sono stati progressi nello sviluppo di hardware specifico per l’inferenza dell’AI, ma molte di queste architetture dividono fisicamente la memoria e le unità di elaborazione. Ciò significa che i modelli di AI sono tipicamente memorizzati in una posizione di memoria discreta e le attività di calcolo richiedono un continuo spostamento di dati tra la memoria e le unità di elaborazione. Questo processo rallenta il calcolo e limita l’efficienza energetica massima raggiungibile.

IBM Research sta studiando modi per reinventare il modo in cui l’AI viene elaborata.

Il computing in-memory analogico, o semplicemente AI analogica, è dal punto di vista di IBM un approccio promettente per affrontare questa sfida, prendendo in prestito le caratteristiche chiave del funzionamento delle reti neurali nei cervelli biologici.

Nel nostro cervello e in quello di molti altri animali, spiega IBM Research, la forza delle sinapsi (che in questo caso sono i “pesi”) determina la comunicazione tra i neuroni. Per i sistemi analogici di intelligenza artificiale, questi pesi sinaptici sono memorizzati localmente nei valori di conduttanza di dispositivi di memoria resistiva su scala nanometrica, come la phase-change memory (PCM), ed esegue operazioni multiply-accumulate (MAC), l’operazione di calcolo dominante nelle DNN, sfruttando le leggi del circuito e attenuando la necessità di inviare costantemente dati tra la memoria e il processore.

Per trasformare il concetto di AI analogica in realtà, sottolinea IBM Research, è necessario superare due sfide fondamentali: questi array di memoria devono essere in grado di calcolare con un livello di precisione pari a quello dei sistemi digitali esistenti e devono essere in grado di interfacciarsi senza problemi con altre unità di calcolo digitali e con un tessuto di comunicazione digitale sul chip dell’intelligenza artificiale analogica.

In un paper pubblicato su Nature Electronics, IBM Research ha compiuto un passo significativo verso la risoluzione di queste sfide, introducendo un chip analogico AI a segnale misto di ultima generazione per l’esecuzione di una serie di compiti di inferenza DNN. Si tratta del primo chip analogico, mette in evidenza IBM, che è stato testato per essere in grado di eseguire compiti di intelligenza artificiale di computer vision come le controparti digitali, pur essendo notevolmente più efficiente dal punto di vista energetico.

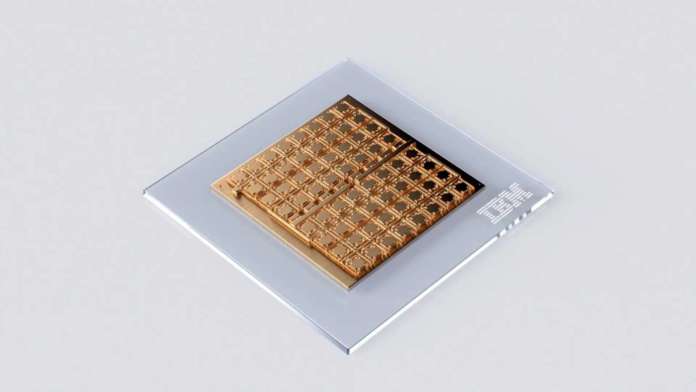

Il chip è stato fabbricato nell’Albany NanoTech Complex di IBM ed è composto da 64 core di analog in-memory compute (o tile), ognuno dei quali contiene una matrice di 256 per 256 unità sinaptiche. In ogni tile sono integrati convertitori analogico-digitali compatti e basati sul tempo per passare dal mondo analogico a quello digitale. Ogni tile è inoltre integrato con unità di elaborazione digitale leggere che eseguono semplici funzioni di attivazione neuronale non lineare e operazioni di scaling.

Ogni tile può eseguire i calcoli associati a un layer di un modello DNN, spiega IBM. I pesi sinaptici sono codificati come valori di conduttanza analogica dei dispositivi PCM. Al centro del chip è integrata un’unità di elaborazione digitale globale che implementa operazioni più complesse, fondamentali per l’esecuzione di alcuni tipi di reti neurali. Il chip dispone anche di percorsi di comunicazione digitale in corrispondenza delle interconnessioni tra tutti i moduli e l’unità di elaborazione digitale globale.

Utilizzando il chip, IBM Research ha eseguito lo studio più completo sulla precisione di calcolo del computing analogico in-memory e ha dimostrato un’accuratezza del 92,81% sul set di dati di immagini CIFAR-10. IBM ritiene che questo sia il livello di precisione più elevato tra tutti i chip attualmente disponibili che utilizzano una tecnologia simile. Nel documento l’azienda ha anche mostrato come sia possibile combinare senza problemi l’elaborazione analogica in-memory con diverse unità di elaborazione digitale e un tessuto di comunicazione digitale. Il throughput per area misurato per moltiplicazioni di matrici input-output a 8 bit di 400 GOPS/mm2 del chip è più di 15 volte superiore rispetto ai precedenti chip di calcolo multi-core in-memory basati su memoria resistiva, pur raggiungendo un’efficienza energetica comparabile.

IBM ritiene dunque di aver dimostrato molti dei building block necessari per realizzare una visione architetturale di un chip acceleratore di inferenza analogica veloce e a basso consumo.

La vision di IBM combina molte analog in-memory computing tile con un mix di core di calcolo digitali special-purpose collegati con una rete 2D massicciamente parallela. Insieme al sofisticato training hardware-aware che IBM ha sviluppato negli ultimi anni, l’azienda si aspetta che questi acceleratori forniscano nei prossimi anni una precisione equivalente a quella delle reti neurali software per un’ampia gamma di modelli.